# Chapter 1

# Monte Carlo methods for massively parallel computers

# Martin Weigel

# Applied Mathematics Research Centre, Coventry University Coventry, CV1 5FB, United Kingdom martin.weigel@complexity-coventry.org

Applications that require substantial computational resources today cannot avoid the use of heavily parallel machines. Embracing the opportunities of parallel computing and especially the possibilities provided by a new generation of massively parallel accelerator devices such as GPUs, Intel's Xeon Phi or even FPGAs enables applications and studies that are inaccessible to serial programs. Here we outline the opportunities and challenges of massively parallel computing for Monte Carlo simulations in statistical physics, with a focus on the simulation of systems exhibiting phase transitions and critical phenomena. This covers a range of canonical ensemble Markov chain techniques as well as generalized ensembles such as multicanonical simulations and population annealing. While the examples discussed are for simulations of spin systems, many of the methods are more general and moderate modifications allow them to be applied to other lattice and off-lattice problems including polymers and particle systems. We discuss important algorithmic requirements for such highly parallel simulations, such as the challenges of random-number generation for such cases, and outline a number of general design principles for parallel Monte Carlo codes to perform well.

# Contents

| 1. | Intro | duction                 | 2 |

|----|-------|-------------------------|---|

| 2. | Para  | llel computing          | ł |

|    | 2.1.  | Performance and scaling | 7 |

|    | 2.2.  | Parallel hardware       | L |

|    | 2.3.  | Algorithmic patterns 19 | ) |

| 3. | Cano  | nical Monte Carlo       | 3 |

|    | 3.1.  | Checkerboard scheme     | 5 |

|    | 3.2.  | Random-hit algorithms   | 2 |

|    | 3.3.  | Cluster updates         | ł |

$\mathbf{2}$

## M. Weigel

|     | 3.4.   | Continuous spins                       | 39 |

|-----|--------|----------------------------------------|----|

| 4.  | Rand   | om number generation                   | 12 |

| 5.  | Gene   | alized ensembles                       | 19 |

|     | 5.1.   | Parallel Tempering                     | 19 |

|     | 5.2.   | Multicanonical simulations             | 51 |

|     | 5.3.   | Wang-Landau update                     | 55 |

|     | 5.4.   | Population annealing                   | 56 |

| 6.  | Disor  | lered systems                          | 58 |

| 7.  | Sum    | nary                                   | 30 |

| Ref | erence | ······································ | 31 |

| Ind | ex     | -                                      | 71 |

# 1. Introduction

The explosive development of computer technology over the past 40 years or so has not only led to pervasive changes of the industrial world and to the way we communicate, learn, work, and entertain ourselves, but it has also enabled an impressive success story of computational sciences.<sup>1</sup> In condensed matter and statistical physics, numerical methods such as classical and quantum molecular dynamics,<sup>2</sup> density functional theory<sup>3</sup> and Monte Carlo simulations<sup>4</sup> were initially developed in the late 1950s and early 1960s when the first digital computers became available. Before that, the tool set of theoretical physics was restricted to exact solutions for sufficiently simplified systems, mean-field type theories neglecting fluctuations, and perturbative methods such as the  $\epsilon$  expansion and high-temperature series. Due to the limited computational power available, numerical techniques were not yet quite competitive, and some researchers considered them as inferior crutches for people allegedly lacking the brilliance for analytical work. It is very rare indeed that one hears such opinions expressed today, and simulations are now firmly established as an indispensable scientific method, a third pillar supporting the building of science besides those of experiment and analytical theory.<sup>4</sup>

This success is the result of two parallel developments: the enormous increase of computational power by a factor of at least  $10^7$  since the first digital computers appeared,<sup>5</sup> but no less the development of ever more sophisticated simulation and other computational methods enabling calculations that were unfeasible with simpler techniques. For simulations in statistical physics the focus of advanced methods has been the study of systems experiencing phase transitions and critical phenomena as well as other effects of complexity such as exotic phases with slow relaxation. Here, one should name cluster updates<sup>6,7</sup> that are effective in beating critical slowing

down close to continuous phase transitions, multicanonical simulations<sup>8,9</sup> that allow to sample the suppressed co-existence region in systems undergoing first-order phase transitions, and exchange Monte Carlo<sup>10,11</sup> that is currently the workhorse for simulations of systems with complex free energy landscapes such as spin glasses, but also methods of data analysis such as histogram reweighting and advanced methods of error analysis.<sup>12,13</sup> Only combining both strengths, i.e., using advanced algorithms on sufficiently powerful hardware enables computer simulation studies to achieve the level of detail and precision required today.<sup>a</sup>

On the computational side, the high-performance computing (HPC) setups available today are highly parallel in nature, and no further significant increase of serial execution speeds of silicon based computing can be expected.<sup>16</sup> Some of the best performance results, especially in terms of FLOPs per Watt, are now achieved by parallel accelerator devices such as GPUs, Intel's Xeon Phi and FPGAs. For computational scientists one of the most pressing current challenges is hence the efficient implementation of existing algorithms on such massively parallel hardware, but also, if possible, the design of new algorithms particularly well suited for highly parallel computing. The purpose of the present chapter is to provide some guidance for the practitioners of Monte Carlo methods particularly in statistical physics as we are moving further into the era of parallel computing. The focus is on simulations of spin models on graphics processing units and using a wide range of algorithms, but we will see that many of the general concepts and design principles are also useful for simulations of different lattice and continuum models and for different hardware such as MPI clusters and Intel's Xeon Phi family of co-processors.

The rest of the chapter is organized as follows: Section 2 discusses the necessary background in parallel computing, including some standard algorithmic patterns for efficient parallelism, as well as the relevant parallel hardware including, in particular, an outline of the most important architectural features of graphics processing units. In Sec. 3 we discuss implementations of standard local-update algorithms, such as the Metropolis and heatbath updates for the example of discrete spin models. While these can be realized rather straightforwardly using domain decompositions, we

<sup>&</sup>lt;sup>a</sup>Consider, for instance, the problem of simulating the two-dimensional Ising model. The Metropolis algorithm has a dynamical critical exponent of z = 2.17(1),<sup>14</sup> while a recent estimate for the exponent of the Swendsen-Wang algorithm is z = 0.14(1).<sup>15</sup> Assuming scaling amplitudes of approximately one in the law  $\tau \sim L^z$  of the autocorrelation times, this results in an algorithmic speedup of  $2 \times 10^7$  for a realistic system size L = 4096, well comparable to the total increase in computational power in the past 40 years.

4

## M. Weigel

next turn to non-local cluster algorithms that are more difficult to parallelize efficiently as they operate on clusters that percolate at the critical point. Finally, we discuss the specific problems of simulating systems with continuous variables on GPU, that arise due to the performance penalty paid for double precision floating point arithmetics on such devices. Section 4 is devoted to a discussion of random-number generation in highly parallel environments, where the availability of a large number of uncorrelated streams of random numbers is required. In Sec. 5 we turn to parallel implementations of generalized-ensemble simulations, discussing the cases of parallel tempering, multicanonical and Wang-Landau simulations, and a variant of so-called sequential (non Markov-chain) Monte Carlo known as population annealing<sup>17,18</sup> that has recently attracted some attention.<sup>19</sup> Section 6 is devoted to a discussion of the specific challenges and opportunities that are held by parallel machines for the treatment of systems with random disorder, where the necessary quenched average provides the possibility for embarrassingly parallel implementations. Finally, Sec. 7 contains our conclusions.

# 2. Parallel computing

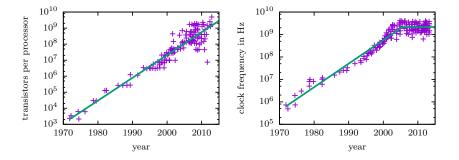

Gordon Moore's prediction from 1965 of a doubling of the number of transistors every two years has been a surprisingly accurate description of the development of integrated circuits over the last four decades.<sup>5</sup> Figure 1 (left) illustrates this for the case of Intel CPUs showing an increase by 7 orders of magnitude from about 1000 transistors in 1970 up to almost  $10^{10}$ transistors today. Although there are clearly physical limits to this development, these are not yet seen in processors today and hence the development can be expected to continue unabated for a while. Another characteristic of computer processors, however, the clock frequency, which for decades showed an equally dynamic increase, started to settle down at around 3 GHz in 2003, see the data of historic CPU clock frequencies shown in the right panel of Fig. 1. It turns out that an increase of clock frequencies beyond a few GHz is not practically feasible for commodity hardware, mostly because the electrical power consumption increases dramatically with the frequency<sup>b</sup> and there is a natural limit to the maximal power density that can be dissipated with conventional cooling methods. Due to the leveling

<sup>&</sup>lt;sup>b</sup>The dynamic power consumption is in fact given by  $P \propto V^2 f$ , where V is the operating voltage and f the frequency.<sup>20</sup> Since, however, the highest operating frequency f is itself proportional to the voltage V, in total  $P \propto f^3$ .

5

#### Monte Carlo methods for massively parallel computers

Fig. 1. Left: number of transistors on commodity processors as a function of their release year. The line shows a pure exponential fit to the data, illustrating the validity of Moore's law.<sup>5</sup> This fit implies a doubling about every 2.1 years. Right: clock frequencies of the same CPUs, showing the leveling off of (approximately exponential) frequency increases around 2003. The data are adapted from Ref. [20].

off of clock frequencies, but also through further effects including limitations in exploiting instruction-level parallelism and the fact that speeds of memory technologies have not developed as dynamically as those of processing units, recently there has been hardly any relevant improvement in the speed of serial programs on standard processors. For decades, scientific and application programmers have been in the comfortable situation that the same serial program could be run on a series of generations of processors and its speed would improve exponentially according to Moore's law, thus allowing scientists to study ever larger system sizes and all users to process bigger data sets with the same codes as time progressed. This development has now come to an end.

The way that Moore's law continues to hold while serial performance has reached a limit is, of course, through the introduction of more and more parallel cores. Typical CPUs are now multi-core with up to a few ten cores, accelerator devices such as Intel's MIC (Xeon Phi) architecture are manycore with dozens to hundreds of cores and GPUs offer several thousand cores in one device. In short, all computers are now parallel, from multicore processors in mobile phones up to the top machines in the TOP500 list of supercomputers with millions of cores.<sup>21</sup> Consequently, programs that make efficient use of present-day machines must be parallel codes. While modern compilers have some capabilities of automatic parallelization, these are quite limited and they will typically not generate code that scales well on machines with different numbers of cores. Apart from any shortcomings in the compilers themselves, this is mainly a consequence of the serial nature

of the prevalent programming languages themselves which produce what could be called implicit serialism: if a task requires several different steps, these must be written in sequence in a serial language, for example as a list of function calls; a compiler cannot always decide whether such steps are independent and hence could be performed in parallel, or whether some of them have side effects that influence the other steps. Similarly, loop constructs cannot be parallelized automatically when they contain pointer arithmetic or possibilities for overlapping index ranges. Other examples occur for sums or more general reductions involving floating-point numbers: due to the limited accuracy such operations are not commutative, and a reordering of the sum will lead to a (most often slightly) different result, typically disabling automatic parallelization to ensure consistency, although the ensuing rounding differences might be perfectly acceptable in a given application. Programs in serial languages and the tools to process them contain many such serial assumptions. As today programming is in fact parallel programming, it is crucial to get rid of the implicit assumption of seriality in thinking about algorithms and augment if not replace the wellknown serial algorithmic building blocks (such as iteration, recursion etc.) by parallel ones (such as fork-join or scatter).<sup>20</sup>

A variety of parallel programming languages or language extensions have been proposed to support this transition. MPI is the de facto standard for distributed memory machines such as cluster computers.<sup>22</sup> OpenMP is very popular for shared memory machines such as single nodes with (one or several) multi-core processors, especially for applications in HPC. Its explicit representation of threads allows fine control in specific situations, but a single code will typically not scale well across many different types of hardware ranging from embedded systems to supercomputers. This goal is more easily achieved using language extensions such as Threading Building Blocks (TBB), Array Building Blocks (ArBB), or Cilk Plus.<sup>20</sup> Finally, frameworks for accelerator devices, in particular GPUs, include the vendorspecific Nvidia CUDA toolkit as well as OpenCL.<sup>23</sup> A detailed discussion of different programming models is clearly outside of the scope of the present chapter and the interested reader is referred to the literature, for instance the excellent Ref. [20]. Although there are many differences between these approaches, a general goal of any such framework must be the creation of scalable code that is able to run efficiently on any amount of parallel hardware and in a performance portable manner, promising decent efficiency also on the next generation of machines. Other desirable features are *com*posability, i.e., the possibility to use all language features together in the

same code, as well as *determinism*, i.e., a guarantee that each invocation of the program leads to identical results. The latter feature is very useful for testing and debugging purposes and it is natural for serial codes, but in some cases it might be difficult to achieve (and detrimental to performance) in parallel programs where the scheduling of individual threads is typically outside of the programmer's control.

The two basic strategies for parallelization are data parallelism and functional decomposition. While the latter can create a limited amount of parallel work, it is clear that only data parallelism, for example in the form of domain decomposition, creates a number of tasks that scales with the size of the problem. This will also be most often the type of parallelism encountered in simulation codes where different parts of the system are assigned to different threads. Functional parallelism, on the other hand, could occur in the present context for complex simulations on heterogeneous machines with accelerators, where only parts of the calculations (for example force-field evaluations) are offloaded to the accelerators and the remaining computations are run on the host machine.<sup>24</sup> It is sometimes also useful to distinguish regular and irregular parallelism, where the regular kind has predictable and regular dependencies such as for the case of matrix multiplication, while irregular parallelism could occur in a parallel evaluation of a search tree through a branch-and-bound strategy, such that some branches and hence parallel tasks are terminated early through the bounding step. As we will see below in Sec. 3.3, irregular parallelism occurs in the tree-based methods for cluster updates of spin models. In terms of mechanisms, parallel computation can be through threads or through vector parallelism. Threads have a separate control flow, while vector calculations apply the same instructions to a vector of data elements in parallel. Clearly, thread parallelism can emulate vector parallelism. As we shall see below for the case of GPUs, vector parallelism can also emulate thread parallelism through the masking out of operations for some of the data elements (lanes) of the vector (Sec. 2.2). Such vector parallelism hence creates pseudo-threads sometimes called fibers.

## 2.1. Performance and scaling

Ideal parallel programs will run efficiently on a wide range of hardware with possibly very different numbers of cores. Code that achieves such performance portability cannot explicitly depend on the features of particular hardware, for example its specific memory hierarchy. This approach can

8

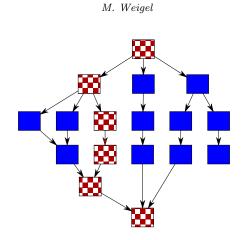

Fig. 2. Example of the steps in a computation represented as an acyclic, directed graph of task dependencies, assuming the same duration for each task. The total number of tasks, 17 in the example, corresponds to the work in the computation, while the longest path from start to end configuration, 6 in the present example, is the span of the algorithm (hatched squares).

achieve good but generally not optimal performance. In HPC applications, on the other hand, it is often admissible to be somewhat more specific to a class of hardware and thus use a larger fraction of the available peak performance. In most cases, however, taking the right general design decisions will contribute significantly more to achieving good performance than machine-specific optimizations.

The limiting factors for parallel performance are (data and control) dependencies between tasks and the communication required between them. A good framework for estimating performance is the *work-span model* :<sup>25</sup> if one represents the necessary steps of a calculation in an acyclic, directed graph of tasks with edges encoding the dependencies, the span is the time it takes to perform the longest chain of instructions that cannot be parallelized (possibly including the effects of synchronization and communication overheads). This is illustrated in Fig. 2. The span limits the possible parallel speedup and, consequently, reducing the span is arguably the most important step towards an efficient parallel program. This could be through the removal of implicit serialism, i.e., getting rid of assumed dependencies that are unnecessary, or through more profound reorganizations of calculations. Apart from the goal of reducing an algorithm's span, the two most profound considerations when performance optimizing a parallel application are data locality and parallel slack:<sup>20,23</sup>

- Data locality: memory accesses that are closer together in time and space are cheaper. Fetching close-by memory locations together makes the best use of bus bandwidth, reusing close-by data makes the best use of caches. As a general rule, memories that are further remote from the compute units have slower connections and higher latencies, so memory transactions should be restricted to local memories as much as possible. This might involve choosing chunk sizes that fit into cache, the reorganization of the memory layout to ensure that subsequent accesses are to nearby locations, or padding to achieve the required memory alignment. As memory transactions are so expensive, it is important to ensure sufficient arithmetic intensity of computations — sometimes it is cheaper to recompute intermediate results than to read them from memory.

- **Parallel slack**: providing more parallel tasks than cores are available improves efficiency. It might be tempting to break a problem into exactly as many threads as can be run in parallel on the available hardware, but this is typically not optimal. Having more threads than cores allows the scheduler to hide memory latencies by putting thread groups waiting for memory accesses into a dormant state while reactivating other thread groups that have received or written their data. In general, it is best to break the calculation into the smallest units that can still amortize the overhead of scheduling a thread.

The main aspects of computational performance concern *latency*, i.e., the total time it takes to finish a single calculation, as well as *throughput*, i.e., the rate at which a sequence of calculations can be performed. Increasingly, also the power consumption of a calculation is considered as a separate performance metric.<sup>26</sup> Depending on the application, the reduction of latency or the improvement of throughput might be the main goal of optimization. The most common metric is the *speedup in latency*,

$$S_p = \frac{T_1 W_p}{W_1 T_p},$$

where  $T_1$  ( $T_p$ ) is the latency and  $W_1$  ( $W_p$ ) denotes the workload of the problem with one worker (p workers). The speedup per worker,  $S_p/p$ , is known as *parallel efficiency* which indicates the return on adding an additional worker. Clearly, the ideal efficiency is 100% corresponding to linear speedup, although in some unusual circumstances one finds  $S_p/p > 1$  due, for example, to cache effects. In determining parallel speedup, one should

compare to the best serial program available, even if it uses a different algorithm. The corresponding absolute speedup arguably provides a fairer comparison than the relative speedup of running the parallel code with just one thread. In a similar way one can also define and analyze the speedup in throughput. An essential aspect of parallel performance theory relates to the scaling of performance with p. Two important limits relate to the cases of a fixed amount of work W performed with a variable number p of processors, corresponding to *strong scaling*, and the situation where the problem size and hence the amount of work are scaled proportional to p, known as *weak scaling*. In the strong scaling scenario with work W, the latency of the serial program is proportional to W,  $T_1 = tW$ . If we assume that the work decomposes into parallelizable and intrinsically serial parts,  $W = W_{\text{par}} + W_{\text{ser}}$ , the latency for the parallel execution satisfies  $T_p \geq t(W_{\text{ser}} + W_{\text{par}}/p)$  and hence the maximal parallel speedup is limited by

$$S_p = \frac{T_1 W}{T_p W} \le \frac{W_{\text{ser}} + W_{\text{par}}}{W_{\text{ser}} + W_{\text{par}}/p}.$$

If the serial part makes up a constant fraction f of the work,  $W_{\text{ser}} = fW$ and  $W_{\text{par}} = (1 - f)W$ , we have

$$S_p \le \frac{1}{f + (1 - f)/p} \tag{1}$$

and hence the speedup is limited by  $S_{\infty} \leq 1/f$  such that, for example, an algorithm that has 10% intrinsically serial calculations cannot be sped up beyond a factor of ten, no matter how many cores are available. Eq. (1) is known as Amdahl's law.<sup>27</sup>

In practice, problem sizes are often scaled with the number of available cores, and so the assumption of constant work might not be appropriate. If, instead, the parallel work increases proportional to p, i.e.,

$$W_p = W_{ser} + pW_{par} = fW_1 + p(1-f)W_1,$$

where it was again assumed that the not-parallelizable work makes up a fraction f of  $W_1$ , and we consider the work done in a fixed time budget T, the speedup in latency becomes

$$S_p = \frac{TW_p}{TW_1} = f + (1 - f)p,$$

(2)

which is asymptotically proportional to p as  $p \to \infty$ . The relation of Eq. (2) is referred to as Gustafson-Barsis law for weak scaling.<sup>28</sup>

A more fine grained analysis of parallel performance of algorithms is possible in the work-span model outlined above. There, the time for one worker,  $T_1 = tW$ , is called the work, choosing units such that t = 1 for simplicity. The time  $T_{\infty}$  for an infinite number of workers is called the span. It corresponds to the length of the longest chain in the execution graph for an infinite number of workers. We easily see that  $S_p \leq p$ , so super-linear speedup is impossible in this model. On the ideal machine with greedy scheduling, adding a processor can never slow down the code, such that

$$S_p = \frac{T_1}{T_p} \le \frac{T_1}{T_\infty},$$

so the speedup is limited by the ratio of work and span. If the work consists of perfectly parallelizable and imperfectly parallelizable parts, the latter will take time  $T_{\infty}$ , irrespective of p. The former then takes time  $T_1 - T_{\infty}$  when using one worker and, as it is perfectly sped up by additional cores, time  $(T_1 - T_{\infty})/p$  with p workers. As at least one worker needs to be dealing with the imperfectly parallelizable part, this provides an upper bound known as Brent's lemma,<sup>20</sup>

$$T_p \le (T_1 - T_\infty)/p + T_\infty,$$

which provides a *lower* bound on the parallel speedup. From this, a good practical estimate for  $T_p$  can be derived noting that for problems suitable for parallelization we must have  $T_1 \gg T_{\infty}$  and hence

$$T_p \approx T_1/p + T_\infty$$

.

Hence it is clear that the span is the fundamental limit to parallel scaling. From Brent's lemma one derives that if for  $S_{\infty} = T_1/T_{\infty} \gg p$ , i.e., if the theoretical maximal speedup is much larger that the actually available parallelism, the speedup is approximately linear,  $S_p \approx p$ . Hence it is good to have sufficient *parallel slack*, a standard recommendation is  $S_{\infty}/p \geq 8$ . This is called over-decomposition.

# 2.2. Parallel hardware

While a number of general design principles, most notably the concepts of data locality and parallel slack outlined above, will contribute to good performance of parallel programs independent of the hardware, a substantial fraction of the peak performance can typically only be achieved with some tailoring to the hardware to be used.

A common classification of parallel processing paradigms relates to the way that control flow and data are combined:<sup>29</sup> single instruction, single data (SISD) setups correspond to standard serial processing; single instruction, multiple data (SIMD) approaches imply vector processing with an array of functional units performing identical calculations on different data elements; multiple instruction, multiple data (MIMD) corresponds to separate instruction streams, each applied to their own data sets — this is implemented in a cluster computer. Another classification concerns memory organization: in shared memory machines each compute element can access all data, whereas in distributed memory setups this is not possible. Cluster machines are examples of the latter type, where data between different nodes can only be accessed after explicitly communicating it between them. Each node, on the other hand, will typically feature several cores that operate a shared memory setup between them.

Parallelism occurs in current hardware at many different levels. At the scope of a single CPU core there is instruction-level parallelism in the form of superscalar execution of serial instructions, through hardware multithreading and vector instructions in extensions such as SSE and AVX. These features are generally hard to configure explicitly unless programs are written in assembly language, and they will often only be activated through certain compiler optimizations. Modern CPUs come with multiple cores and hence can run multiple, and possibly many, threads. Such parallelism is typically only accessible to programs that are explicitly parallel, using multi-threading language extensions such as OpenMP, TBB, ArBB or Cilk Plus. To ensure good performance, data locality needs to be respected, and it is hence important to understand the memory hierarchy of multi-core CPU systems: the functional units are equipped with a moderate number of very fast registers, and a cascade of cache memories (typically L1, L2 and L3) translates accesses down to the main memory of the machine. In general, bandwidths decrease and latencies increase as the hierarchical (and thus the physical) distance of memory locations to the compute units increases. Caches are typically organized in lines of 64 or 128 bytes, and each access to main memory fetches a full cache line, thereby accelerating accesses to nearby memory locations. Only coherent accesses therefore allow to achieve transfer rates close to the theoretical memory bandwidths. Finally, there is also a virtual memory system underneath the actual physical memory, swapping pages of unused memory out to disk as required, and a lack of memory locality will lead to frequent page faults that are immensely expensive on the timescale of the CPU clock.

13

## Monte Carlo methods for massively parallel computers

A relatively recent addition to the arsenal of parallel hardware are accelerator devices such as GPUs, Intel's MIC (many integrated core) processors, and field-programmable gate arrays (FPGAs). GPUs and MIC devices provide a large number of relatively simple compute cores packaged on a separate device which is used to offload expensive calculations that are well suited for parallel execution. While GPUs use specific programming models (see below), the Intel MIC architecture appears to the user like a standard multi-core system with particularly many cores (currently around 60), supporting most of the standard development tool-chain. FPGAs, on the other hand, are integrated circuits that can be reconfigured on demand to implement an algorithm in hardware. While traditionally, this could only be achieved by experts in circuit development using a hardware description language, it is now possible to use general-purpose programming languages (with suitable extensions) to configure FPGAs, for example OpenCL.<sup>30</sup> For particular parallel applications, FPGAs can provide higher performance at a lower power consumption than any other parallel hardware.

GPUs operate at a sweet spot of parallel computing in that they provide very substantial parallelism with the availability of several thousand parallel hardware threads, but without requiring an expensive distributed memory machine such as a cluster computer. As most of the implementations presented in the application part of this chapter have been realized for GPUs, we discuss their architecture in somewhat more detail here. Clearly, GPUs have been designed for the efficient rendering of (mostly 3D) computer graphics, a task that involves the parallel manipulation of many 3D objects, the mapping of textures, and the simultaneous projection of a scene onto the millions of pixels in an image frame. Driven by the large sums of money available through the gaming industry, GPUs are hence highly optimized to perform well for these massively parallel and very predictable tasks. For a number of generations, their peak performances have substantially exceeded those of CPUs released at the same time, with the recently announced Volta generation V100 Nvidia GPU promising a single-precision floating point performance of up to 15 TFLOPs per device. The main reason for this lead in performance is a difference in design goals: current CPUs are optimized to deliver the best possible serial performance under an unpredictable, interactive load. To achieve this, a large proportion of the available die space is devoted to pipelining, branch prediction, and similar control logic that helps to improve single-thread performance, as well as a hierarchy of relatively large cache memories that are required since locality of memory accesses under a mixed interactive load cannot be ensured. GPU

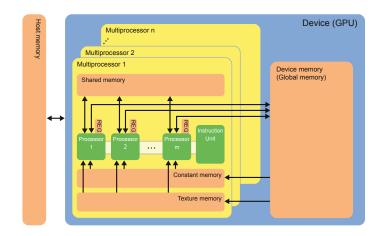

Fig. 3. Schematic of the architecture of GPU devices, using the terminology of Nvidia CUDA.

dies of the same complexity, on the other hand, feature a much larger number of actual compute units, much lighter control logic and smaller cache memories. In an interactive load situation they would not perform well, but for repetitive and highly parallel calculations they can deliver exceptional performance. This makes them ideal vehicles for general-purpose scientific calculations (GPGPU).<sup>31</sup>

The two main players in the high-end GPU market are Nvidia and AMD. Although the actual performances of corresponding boards from both vendors are about similar, Nvidia GPUs are much more firmly established as accelerator devices in HPC. This is, in part, due to a rather well developed eco-system of development tools, and supporting application libraries. The standard model for programming Nvidia GPUs is through the proprietary CUDA framework,  $3^{32}$  providing a C/C++ language extension with the associated compiler, performance analysis tools and application libraries. Less machine specific frameworks such as OpenCL and OpenACC are also available, and can also be used for programming AMD GPUs. Due to limitations in the accessible features and a lack of fine-grained control they are somewhat less popular for Nvidia GPUs applied in HPC, but they provide portable code that can run on GPUs of different vendors and even multi-core CPU systems. Figure 3 shows a schematic of the general layout of a GPU device. It consists of a number of multi-core processors (known as "streaming multiprocessors" for Nvidia devices) with the associated local, shared *memory* and a common *global memory* per device. The number of cores per

# Host (CPU) Device (GPU) Final Final Final Block (0,0) Block (1,0) Block (2,0) Thread Thread Thread (0,0) Thread Thread Thread Thread Thread (0,1) Thread

#### Monte Carlo methods for massively parallel computers

Fig. 4. Execution configuration of device code in the form of a grid of thread blocks.

multiprocessor is between 32 and 192 in Nvidia cards ranging through the Fermi, Kepler, Maxwell, and Pascal series, and each GPU card comes with a few tens of multiprocessors, thus totaling in several thousand cores for the larger cards. The associated compute model features elements of SIMD and MIMD systems which sometimes is called single instruction, multiple threads (SIMT). It corresponds to a tiled SIMD architecture, where each multiprocessor has SIMD semantics, but the vector lanes are promoted to fibers with the possibility of divergent control flow through the masking out of lanes for branches that they do not take. These threads are very lightweight and the overhead for their scheduling is minimal. As groups of 32 threads (a *warp*) are scheduled together on a single SIMD processor, it is important to minimize thread divergence using masking as it severely impedes performance.<sup>23</sup>

The main control flow of programs in CUDA (and similarly for OpenCL) is executed on CPU, and it contains particularly labeled device functions (known as *kernels*) that offload specific calculations to the GPU device. The particular arrangement of threads to be used for a kernel invocation is known as the *execution configuration*, and it describes a grid of thread blocks. This is illustrated in Fig. 4. Each block is scheduled to execute on a single SIMD processor. Its threads can communicate (and synchronize) via the shared memory area local to it. Threads in different blocks cannot directly communicate, and synchronization of all threads in a grid

can only happen through returning to CPU code.<sup>c</sup> More recent cards and driver versions also allow for dynamic parallelism, where additional threads can be spawned from within kernel code.<sup>33</sup> The most important available memories are illustrated in Fig. 3. Moving from registers through shared memory to global memory, the latencies for accesses increase dramatically and the bandwidths decrease correspondingly. Additionally, Nvidia cards feature L1 and L2 caches also. While these have the usual associative cache line behavior, shared memory is allocated and managed explicitly by the threads in a block. It is fast but very small, at most 48 KB per block, so must be used wisely. GPU devices can only be run as accelerators attached to a CPU node. They are connected through the PCI-e bus and any data that is required as input or output must be transferred from the CPU to the GPU main memory explicitly. This is of particular importance for hybrid codes that perform part of the calculations on CPU and for multi-GPU programs. Such transfers can be interleaved with calculations, however, and in some cases this allows to completely hide these memory transfer latencies. As an extension, it is also possible to enable a unified virtual address space, such that the same pointers can be used across CPU and GPU memories, and data are automatically transferred across the PCI bus as required by the access patterns.

It is not possible in the framework of the present chapter to provide a comprehensive discussion of programming models for GPUs and, in particular, give an introduction to the CUDA or OpenCL language extensions. A number of good books and online resources fill this gap, see, e.g., Refs. [23,33–35]. It will suffice for the present purposes to provide a list of issues to consider in order to achieve good performance, roughly in the order of their relevance:

• Memory coalescence: each cached access to global memory fetches or writes a full cache line of 128 bytes. If only a single 4-byte word of this data is actually used, the efficiency of bus usage is extremely poor. In ideal access patterns, the 32 threads of a warp access memory locations in the same 128 byte cache line, leading to 100 % efficiency of memory accesses. The actual performance penalty for misalignment depends on whether accesses are cached in L1 (128 byte cache lines) or in L2 only (32 byte segments).

$<sup>^{\</sup>rm c}$ Note that there are some advanced features allowing for limited communication between different blocks from within a kernel, including atomic operations as well as memory fence functions. For details see the CUDA C Programming Guide.<sup>33</sup>

Improving memory coalescence implies good data locality and will typically involve rearranging multi-dimensional arrays in memory such that the fastest-changing index corresponds to neighboring threads in a block.

- **Parallel slack**: accesses to shared memory typically take tens of clock cycles, accesses to global memory at least hundreds of cycles. These memory latencies can be hidden away by the scheduler if there is enough parallel slack. Once a warp issues a high-latency memory transaction, it is taken off the compute units into a dormant state and another warp with completed memory transaction is activated instead. As a rule of thumb, optimal performance is achieved with a parallel slack of at least 8–10 times the number of available cores, implying several ten thousand threads per grid on high-end GPUs.

- Occupancy: There are limits to the total number of resident threads (2048 on recent Nvidia cards) and the total number of blocks (16–32) per SIMD processor. Additionally, the number of registers per thread requested by a given kernel can further limit the total number of threads and blocks that can be assigned to a multiprocessor at any given time. To the extent that a limitation in register usage does not impede performance, maximum throughput is typically achieved by maximizing the occupancy of threads on each SIMD processor.<sup>d</sup> Also, it is generally best to choose the total number of blocks to be a multiple of the number of SIMD processors of the device used.

- Shared memory: explicit caching of data in shared memory can lead to massive performance improvements compared to direct accesses to global memory. Advantages will be larger the more often data loaded into shared memory are reused. A common pattern is to load a tile of the system into shared memory, update it there and then write the result back to global memory. For best performance, the different threads in a warp need to access shared memory locations in different banks to avoid bank conflicts.<sup>34</sup>

- Arithmetic density and data compression: as the arithmetic peak performance of GPU devices is enormous, many codes are limited by the practically achieved bandwidth of memory transfers, i.e., moving the data to and from the compute units. If this is

$<sup>^{\</sup>rm d}$  The CUDA toolkit provides an occupancy calculator spreadsheet to help determine the right parameters.  $^{32}$

the case, the optimization strategy must be a combination of improving memory throughput and reducing the amount of data that needs to be transferred. Throughput can be mainly improved by ensuring coalescence of memory accesses. A reduction of memory transfers results from a good use of shared memory and caches, but also from the most compact storage of data. If, for instance, a dynamic degree of freedom is an Ising spin corresponding to one bit of information, it is wasteful on memory bandwidth to store it in a 32-bit word. Instead, it should be stored in an 8-bit variable or several spins should be packed as individual bits into a longer word. In a situation where performance is memory bound, it should be attempted to increase the arithmetic intensity of the relevant kernel. For instance, it can be beneficial to recalculate intermediate results instead of re-reading them from (or even storing them in) main memory.

- Floating-point calculations: Floating-point operations in double precision are significantly more expensive on GPUs than singleprecision calculations. The typical performance penalty for using double precision ranges between two and eight on recent Nvidia cards, where the best double precision performance is only available on the much more expensive Tesla series of GPGPU cards, but not on the otherwise very similar gaming and consumer cards. On CPUs such effects are typically not as pronounced. In practice the speed of many programs will not be only determined by floating-point performance, such that the overhead for using double precision might be less dramatic than indicated above. In general sticking to single precision or some form of mixed precision calculations, where some intermediate results are stored in single (or even half) precision and only sums over large numbers of elements use double (or higher) precision, can be useful strategies. Another aspect of floating-point performance on GPUs is the availability of hardware units for the evaluation of certain special functions such as square roots, exponentials, logarithms and trigonometric functions in single precision.<sup>23</sup> These have somewhat reduced precision but much higher performance than the software versions.<sup>36</sup>

- **Thread divergence**: The individual SIMD processors emulate threads by masking out vector lanes to which a certain code branch does not apply. For a conditional, this means that all branches are evaluated serially with all threads to which the current branch does

not apply masked out. Having n branches with the same computational effort hence increases the worst-case total runtime (at least) by a factor of n. Since scheduling happens on the level of warps (of 32 threads on Nvidia cards), it will improve performance if it can be ensured that all threads of a warp take the same execution branch as otherwise the different paths will be serialized. In particular, one should avoid the use of block-wide thread synchronization in divergent code as it will slow down the execution of all warps.

As we shall see for some of the examples below, taking the above optimization considerations into account can turn a very moderate GPU speedup against serial code which is comparable to that achievable by parallelizing the CPU code into a several hundredfold speedup against the serial program.

# 2.3. Algorithmic patterns

It is not possible within the scope of the present chapter to discuss in detail general parallel algorithms and their implementation with the help of the available language extensions such as MPI, Cilk Plus, or CUDA. To help avoid running into the ubiquitous *serial traps*, i.e., unnecessary assumptions in coding deriving from the general serial execution assumption commonplace until recently, and to ease the transition from a serial to a parallel mindset required now for practitioners developing computer simulation codes, it appears useful, however, to provide an overview of the most pertinent general algorithmic *patterns* or algorithm skeletons.<sup>37</sup> To this end we follow closely the excellent exposition in Ref. [20].

The most basic pattern, which applies to serial and parallel programs alike, is the ability to stack patterns, i.e., to replace a certain task in an algorithmic pattern by another pattern and to do so hierarchically up to an essentially arbitrary recursion depth. This ability, which is equivalent to the composability of functions in mathematics, is called *nesting*. In serial computing, nesting is mostly straightforward: the body of a loop, for example, can contain another loop or a conditional statement etc. In parallel algorithms problems can arise when the nesting is allowed to be dynamic, i.e., it grows with the size of the problem. This can create an unbounded number of parallel threads as the input size increases, such that efficient implementations need to decouple the potential parallelism resulting from the nested algorithm from the actually available hardware parallelism.

## 2.3.1. Control flow

A natural distinction arises between control flow patterns and data management patterns. Regarding control flow, serial patterns are rather straightforward and mostly correspond to the elementary features available in most (procedural) languages. The sequence pattern expresses the sequential execution of several tasks. Although there might not actually be any dependence between the elements of a sequence, a serial program will always execute them in the given order. Optimization phases of compilers and even the control logic of modern processors ("out-of-order-execution") in some cases will change the order of execution in a sequence, however, if their analysis allows to ascertain that the results will be unchanged. The selection pattern corresponds to conditional execution, usually expressed in an if statement. Iteration is the main serial pattern for accommodating variably-sized inputs. A common strategy for parallel computing is the (possibly automatic) parallelization of loops, but in many cases the simplest approaches fail due to data dependencies between the iterations. Finally, the *recursion* pattern (which is absent in some languages such as Fortran 77), can often (but not always) be expressed by iteration also, but sometimes allows for much simpler code. It is the natural match for divide-and-conquer strategies.

Parallel control flow patterns are not quite as universally well known. The basic examples generalize the serial patterns discussed above. If a sequence of tasks is actually independent, fork-join can be used to run them in parallel. After their completion execution returns to a single thread. Typically, such independence is only relative, however, and the results of a task are needed at some point later on in the program, such that some communication of forked threads is required. Typically this is through synchronization points (barriers), where all threads of a certain fork point need to have completed a certain part (or all) of their task. Other parallel control patterns are mostly generalizations of the iteration mechanism. The most important is map, where a function is applied to each element of an index set. This corresponds to a serial loop where each iteration is independent of the others, which is the case that is also handled well by compiler-level parallelization. If the strict independence of elemental operations is relaxed, and each application of the function has access also to certain neighboring elements in the input vector, one speaks of a *stencil*. Here, decomposition of the vector into independent sub-sets (such as for the checkerboard decomposition discussed below in Sec. 3.1) and tiling are

important optimization strategies. The stencil pattern is the work horse of most simulation codes, ranging from lattice systems to computational fluid dynamics. In a *reduction*, the results of applying a function to each element in a set are combined together. The most common combiner functions used here are addition, multiplication, and maximum. Whether the combiner function is associative and/or commutative decides to which degree the result depends on the actual schedule of parallel operations. A typical parallel implementation leads to a tree structure, where partial reductions are formed at each level and passed down to the next level for further reduction. A combination of map and reduction is given by the scan operation, where for each position in the output a partial reduction of the input up to that point is needed. To parallelize it, often additional intermediate calculations are required, thus increasing the total work and possibly limiting the scaling properties of the whole code. Finally, a recur*rence* is a generalization of map and stencil where each iteration can read and write neighboring elements in the vector.

## 2.3.2. Data management

The allocation mechanism used for automatic variables and also for local variables in function calls is *stack allocation*. Since it follows strict last in, first out (LIFO) logic, allocation and deallocation are achieved simply through the stepping of a pointer and all stack data is contiguous in memory. For dynamic or *heap allocation*, on the other hand, there is no prescribed order of allocation and deallocation operations and, as a consequence, the locations of consecutive allocations can be become scattered over distant parts of the actual physical memory, thus limiting performance where it depends on memory locality. In languages that allow it, memory accesses are often through direct read and write accesses using pointers. These can make (in particular automatic) vectorization and parallelization difficult as it typically cannot be ascertained at compile time whether two different pointers refer to the same location in memory or not (a problem known as aliasing).

In parallel codes, data locality is particularly important. In a distributed memory setup, clearly accesses to local memory will be substantially more efficient than requesting data from a different MPI node. An even more fundamental problem is the concurrency of accesses, in particular to avoid race conditions resulting from uncontrolled interleaved read and write accesses to the same locations. In general, it is important to understand whether

a given data element is shared between different workers and when it is not and, as a result, to place it into a memory with the appropriate scope. Some parallel data patterns include *pack*, where a subset of an input vector selected by another, Boolean selection vector of zeros and ones is placed next to each other in a contiguous fashion; *pipelines*, where different stages in a sequence of operations run independently as separate threads each of which delivers partially processed data to the next stage; the *geometric decomposition* mentioned above in the context of the stencil pattern that uses tiles, strips, checkerboards or other suitable geometric domains to be worked on in parallel; and the *gather* and *scatter* pair of operations that use a data vector and a set of indices and either reads (gather) or writes (scatter) in the data vector at the locations given in the index vector.

More advanced patterns such as superscalar sequences or branch-andbound are beyond the scope of the present introduction. They are described in detail in Refs. [20,38].

# 2.3.3. Pitfalls

Before discussing the actual applications of massively parallel computing in computer simulations in statistical physics, it is perhaps useful to summarize again the most common pitfalls of parallel algorithms and the basic approaches for avoiding them.

Race conditions are among the most common and difficult to debug problems in parallel codes. If, for example, two threads try to increment a shared variable, one of the updates can be lost if the read of the second thread occurs after the read of the first thread but before the write operation of the first thread. As the results depend on the typically unpredictable order of execution of individual threads, these problems are often intermittent in nature. If at all possible, the potential for such races should be avoided by choosing suitable algorithms. If this is not possible, races can be tamed by the use of memory fences and locks, which essentially guarantee one set of operations to be finished before the other set starts. Operations on locks must occur atomically, such that they appear instantaneous to other tasks.

*Deadlock* occurs when two or more tasks are waiting for each other to complete certain tasks and each cannot resume until the other task finishes. This can be the case, for example, if several locks need to be acquired by more than one task, each task acquires one of the locks and waits for the other one to become available. It can be avoided if locks are always acquired

by all tasks in the same order, but the problem serves to show that locks are best avoided. Locks also create serial bottlenecks in the code as all operations on a single lock must occur in sequential order. This effect will impede the scaling of an algorithm, but whether this is practically relevant depends on the frequency of use of the lock and the actual number of threads employed.

The other main pitfall in parallel code is a *lack of locality*. Most hardware is built on the assumption that for each memory transaction each core is likely to either use the same or a nearby memory location again in the nearby future (temporal and spatial locality). To avoid problems in this respect, parallel code needs to use a suitable layout of data in memory and make good use of cache memories where they are available. On GPUs this includes the issues of coalescence of memory transactions, the use of shared memory and an appropriate cache configuration as discussed above in Sec. 2.2.

Depending on the parallelization strategy and the nature of the problem, another source of inefficiency arises from *load imbalance* between parallel threads. Apart from suitably changing the parallelization strategy, a fine-grained decomposition of work can help to mitigate the effects of load imbalance. Also, adaptive schemes of idle threads acquiring new work via a scheduler can lead to improvements here. If, on the other hand, the overdecomposition of work is pushed too far, there is a danger of the parallel *overhead* for thread initialization, copying of data etc. to outweigh the scaling gain, especially if the arithmetic intensity of individual threads becomes too low.

# 3. Canonical Monte Carlo

There is by now a very wide range of Monte Carlo methods that are used for simulations of systems in (classical) statistical physics.<sup>4,39</sup> While there are a few exceptions (and we will discuss one below in Sec. 5.4), the overwhelming majority of methods are based on Markov chain Monte Carlo (MCMC) that allows to implement importance sampling and also simulations in generalized ensembles.<sup>40</sup> In this scheme, configurations are modified in each step according to transition probabilities that only depend on the current configuration. The resulting Markov chain of configurations,

$$\{s_i\} \to \{s'_i\} \to \{s''_i\} \to \dots$$

where the  $s_i$  denote the configurational variables, converges to a stationary distribution  $\pi(\{s_i\})$  if the chosen move set is *ergodic* (i.e., loosely speaking,

it allows to connect all pairs of states within a finite number of steps) and the transition probabilities  $T(\{s_i\} \rightarrow \{s'_i\})$  satisfy the *balance* equation

$$\sum_{\{s'_i\}} \pi(\{s_i\}) T(\{s_i\} \to \{s'_i\}) = \sum_{\{s'_i\}} \pi(\{s'_i\}) T(\{s'_i\} \to \{s_i\}).$$

(3)

The simplest way of fulfilling Eq. (3) is to demand equality term by term under the sums,

$$\pi(\{s_i\})T(\{s_i\} \to \{s_i'\}) = \pi(\{s_i'\})T(\{s_i'\} \to \{s_i\}).$$

(4)

This is known as *detailed balance* condition. Together with ergodicity it is sufficient, but in contrast to balance, Eq. (3), it is not necessary to ensure convergence.

There is some further freedom in implementing Eq. (4). The best known approach is the Metropolis algorithm<sup>41</sup> where

$$T(\{s_i\} \to \{s'_i\}) = \min\left[1, \frac{\pi(\{s'_i\})}{\pi(\{s_i\})}\right].$$

(5)

In the simplest method, the proposed configuration  $\{s_i\}'$  only differs from the current one  $\{s_i\}$  in a single degree of freedom, for example the orientation of a spin or the position of a particle. While the scheme is also valid for any other modification rule, any sufficiently non-local update — unless ingeniously crafted<sup>6</sup> — will result in largely different probabilities  $\pi(\{s_i\})$ and  $\pi(\{s_i'\})$  and hence very small move acceptance rates. For the actual implementation it is often useful to decompose the transition probability as  $T(\{s_i\} \rightarrow \{s_i'\}) = C(\{s_i'\}|\{s_i\}) p_{acc}(\{s_i'\}|\{s_i\})$ , where *C* is the proposal probability for a certain move  $\{s_i\} \rightarrow \{s_i'\}$  and  $p_{acc}$  is a move acceptance probability evaluated according to Eq. (5). The proposal probability *C* determines the order in which individual degrees of freedom are tried, the most common approaches being, respectively, a uniformly random spin selection and a sequential selection of spins in successive steps, traversing the lattice in a regular fashion.

Another standard approach for satisfying the detailed balance condition (4) is the heatbath method for the update of a single variable  $s_k$ , where its new value is directly chosen from the equilibrium distribution  $\pi$  conditioned on the given values of the remaining degrees of freedom  $s_i, j \neq k$ :

$$T(\{s_i\} \to \{s'_i\}) = \frac{\pi(s'_k | \{s_{j \neq k}\})}{\sum_{s_k} \pi(s'_k | \{s_{j \neq k}\})}.$$

(6)

If  $s'_k$  only takes values from a finite set of options, sampling from the above distribution is straightforward by using geometric sampling from the cumulative distribution<sup>42</sup>  $\sum_{s'_k=s_{\min}}^{s_{\max}} \pi$  or by using more advanced techniques

such as Walker's method of alias.<sup>43,44</sup> For continuous degrees of freedom the method can be implemented if there is an analytical inversion of the cumulative distribution function corresponding to Eq.  $(6)^{45}$  or by using tables to approximate this expression.<sup>43</sup>

For the examples in this section we will focus on simulations in the canonical ensemble with

$$\pi(\{s_i\}) = \frac{1}{Z_{\beta}} \exp[-\beta \mathcal{H}(\{s_i\})],$$

where  $\mathcal{H}(\{s_i\})$  is the Hamiltonian and  $\beta$  denotes inverse temperature. Note that the partition function  $Z_{\beta}$ , that is in general unknown, drops out of the expressions (5) and (6) for the transition probabilities. Other ensembles, such as NpT or  $\mu VT$  for particle systems, can be realized in a similar way, and we discuss generalized-ensemble simulations in Sec. 5 below.

For definiteness, we first focus on the nearest-neighbor Ising model with Hamiltonian

$$\mathcal{H} = -\sum_{\langle i,j \rangle} J_{ij} s_i s_j - \sum_i h_i s_i.$$

<sup>(7)</sup>

Here,  $J_{ij}$  are the exchange couplings between nearest-neighbor spins and  $h_i$  denotes an external magnetic field acting on the spin  $s_i$ . We initially concentrate on the ferromagnetic model with uniform couplings  $J_{ij} = J = 1$  and in the absence of magnetic fields,  $h_i = 0$ , and come back to the case of disordered systems in Sec. 6. For the purposes of the present chapter, we will always apply periodic boundary conditions as is typically recommended to minimize finite-size effects, but other boundary conditions can be implemented quite easily as well, and the optimizations mentioned here are essentially independent of this choice. Generalizations to models with different finite interaction ranges are rather straightforward and only lead to different decompositions of the lattices into interpenetrating sub-lattices of non-interacting sites. Systems with truly long-range interactions require different methods which are outside of the scope of the present discussion.<sup>46,47</sup>

## 3.1. Checkerboard scheme

Following the algorithm outlined above, a single spin-flip simulation of the Ising model (7) with the Metropolis algorithm comprises the following steps:

(1) Initialize the system, possibly with a uniformly random spin configuration.

- (2) Choose the lattice site k to update, according to the scheme used, either randomly, sequentially or in a checkerboard fashion.

- (3) Calculate the energy change incurred by flipping spin k,

$$\Delta E_k = 2s_k \sum_{j \, \mathrm{nn} \, k} s_j$$

Draw a random number r uniformly in [0, 1). Accept the flip if  $\Delta E_k \leq 0$  or

$$r < \exp(-\beta \Delta E_k),\tag{8}$$

otherwise reject and maintain the current configuration as the new state.

(4) Repeat from step 2 until the prescribed number of updates has been completed.

In a serial implementation, typically random or sequential site selection would be used. Sequential updates lead to somewhat faster relaxation of the chain,<sup>48</sup> which can be understood qualitatively from the possibility to transmit information about spin updates ballistically through the lattice in the direction of sequential progression. Additionally, a sequential update is cheaper computationally than visiting sites in random order as it features good memory locality and it also does not require an additional random number for site selection. Note that sequential updates do not satisfy detailed balance (while still satisfying balance),<sup>40</sup> which needs to be taken into account for studies of dynamical properties.

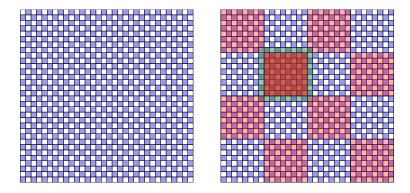

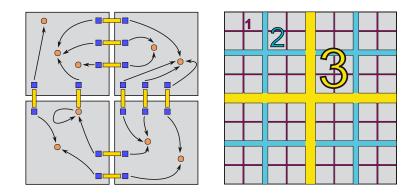

For parallel updates, on the other hand, a suitable domain decomposition of the lattice is required. For bipartite lattices and nearest-neighbor interactions this results in a checkerboard (or generalized checkerboard in three and higher dimensions) labeling of the lattice, which allows different spins on the same sub-lattice to be updated in parallel, independent of each other. This is illustrated for the square lattice in the left panel of Fig. 5. For different lattice types and/or models with different (finite) interaction ranges, similar decompositions can always be found, the only difference being that they in general require more than two sub-lattices. A full sweep of spin updates in this scheme then corresponds to a parallel update of all spins on the even sub-lattice followed by a synchronization of all threads and a parallel update of all spins of the odd sub-lattices. In the maximally parallelized version each spin of one of the sub-lattices is updated by a separate thread, leading to a total of N/2 parallel threads, where  $N = L^d$  is the total number of spins. For a GPU implementation, the restriction in

27

#### Monte Carlo methods for massively parallel computers

Fig. 5. Left: checkerboard decomposition of the square lattice. Right: double checkerboard decomposition of the square lattice. The tiles of  $8 \times 8$  sites are assigned to thread blocks, and red (darker) and blue (lighter) tiles are updated in an alternating fashion. Within each tile, the threads of a block update spins of one sub-lattice, synchronize, and then update the other sub-lattice. The shaded tile and halo indicate the subset of spins that are cooperatively loaded into shared memory by the threads of a block.

the number of parallel threads in a block (1024 for recent Nvidia GPUs) makes it necessary for all but the smallest systems to decompose the lattice using tiles, for which one possibility in 2D is a square shape with  $T \times T$  spins each as shown in the right panel of Fig. 5. Other shapes such as strips can also be used,<sup>49</sup> and the optimal shape depends on the arrangement of spins in memory and the caching mechanisms employed.<sup>50</sup>

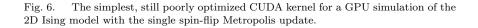

The resulting GPU simulation code is very simple as is apparent from the CUDA implementation of the simulation kernel shown in Fig. 6. The random numbers required for implementing the Metropolis criterion are created via inline instances of generators, one per thread, hidden behind the macro RAN(x). As an evaluation of the exponential function in Eq. (8) is relatively expensive computationally, it is common practice for systems with a small number of states per spin to tabulate the possible values of  $\exp(-\beta\Delta E_k)$ , and this was also done here with the result stored in the array **boltzD**. The sub-lattice is selected using the **offset** variable that should be either 0 or 1, such that the kernel needs to be called twice to achieve a full update, once for each sub-lattice. In this case thread synchronization is achieved through a return of the control to the CPU code in between kernel calls (which are in the same stream), ensuring that all calculations of the first call have completed before the second call is executed.

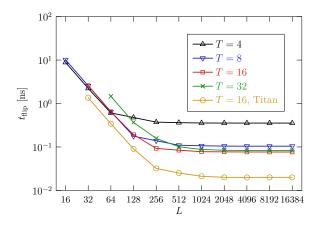

The parallel speedup observed for this code run on a Tesla C1060 card with 240 cores over a serial code run on a CPU of the same period (Intel

28

M. Weigel

Q9650) is about 10-fold. This rather moderate improvement is typical for many of the simplest implementations that do not take many specifics of the architecture into account. In view of the general performance guidelines sketched in Sec. 2.2 a number of improvements come to mind:

• The locality of memory accesses and hence coalescence is not very good in the setup of metro\_checker(). Successive threads in a block update spins that are at least two memory locations apart (for spins in the same row) or even potentially arbitrarily far apart for spins in different rows of the same tile. Also, when calculating the sum over nearest neighbor spins in the variable ide accesses are not coalesced and each spin is read twice as the right neighbor of a spin on the even sub-lattice (say) is the left neighbor of the next spin on the same sub-lattice etc. If the second reads are not served from a cache, they will be as expensive as the first ones. A natural improvement increasing the coalescence of operations on spins to be updated is to store the even and odd sublattices separate from each other, potentially arranging them tile by tile to avoid problems with non-locality of memory accesses in moving from row to row. A further improvement can be achieved by re-shuffling the spins in each sub-lattice in a way such that as many neighbors as possible of a spin on one sub-lattice appear as consecutive elements in the array for the other sub-lattice. A scheme dubbed "crinkling" that ensures that three out of four neighbors are next to each other for the square lattice was proposed in Ref. [51]. A similar, but more general scheme of "slicing" for hypercubic lattices in any dimension is used in Ref. [50]. A "shuffled" <sup>52</sup> or "interlaced" <sup>53</sup> memory layout combines the

separate storage of odd and even sub-lattices for two realizations to further improve coalescence. To reduce the arithmetic load incurred by the required index calculations for spin accesses, one might also bind the arrays for each sub-lattice to a texture.<sup>e</sup>

- The Boltzmann factors are already tabulated in the array **boltzD** to avoid the expensive evaluation of the exponential function. This part can be further sped up by using a texture for storing the array since textures are well optimized for read accesses of different threads of a warp to different locations (which will be the case since the energy changes  $\Delta E_k$  will differ between spins).

- The use of int variables of 32 or 64 bits is wasteful for the storage of the one-bit information  $s_i$  and causes unnecessary data transfer over the bus that can slow down the code. It is straightforward to replace the ints by only 8-bit wide chars which already provides for a noticeable speedup. An additional improvement can be achieved by the use of multi-spin coding (MSC), typically implemented with int variables of 32 or 64 bits, to ensure that each spin only occupies one bit of storage. For the simulation of a single ferromagnetic system, this means that spins located at different lattice sites need to be coded together, and it is typically most efficient to unpack them on GPU for the actual spin update. Some of the details are discussed in Ref. [54]. To achieve results of high statistical quality, it is important in this setup to use independent random numbers for updating each of the spin coded in the same word. A related issue for a simulation method involving a population of configurations is discussed below in Sec. 5.4 in the context of the implementation of the population annealing algorithm.

- It is possible to explicitly disable the use of L1 cache for reads.<sup>f</sup> As a result a cache miss fetches a 32 byte segment and stores it in L2, whereas otherwise an L1 cache line of 128 bytes would be loaded. For the "crinkled" memory setup this tends to increase memory bus efficiency for the neighbor that is not sequentially aligned.

- On some cards it can be advantageous to remove thread divergence and ensure write coalescence by updating the spin variable irrespective of whether the flip was accepted and only deciding about the new orientation in a local variable in the Metropolis condition.

$<sup>^{\</sup>rm e}{\rm Textures}$  are handled in a separate memory hierarchy equipped with additional hardware units for indexing.^32

<sup>&</sup>lt;sup>f</sup>The relevant nvcc compiler switch is -Xptxas -dlcm=cg.

Storing the two sub-lattices separately, using the crinkling transformation, binding the Boltzmann factors to a texture, using chars to store spins, disabling L1 cache and using coalesced writes increases the speedup factor on the Tesla C10560 to about 60. Further improvements can be achieved by using textures for the spin arrays and further optimizations of the memory arrangements and access patterns as described in detail in Ref. [50]. We note that more recent cards are somewhat less sensitive to data locality issues due to improved automatic caching. On the Maxwell card GTX Titan Black, for example, we find spin-flip times of about 0.2 ns for the initial version of the code, corresponding to an about 30-fold speedup compared to an Intel Xeon E5-2620 v3 CPU, whereas the optimizations mentioned above boost this performance to an about 100-fold speedup with  $t_{\rm flip} = 0.06$  ns (L = 4096).

An alternative optimization strategy lies in the use of shared memory by loading tiles of the configurations into this fast cache:

- Storing the spin configuration of the tile that is currently being updated in shared memory allows to avoid problems with non-coalescence of global memory accesses as well as the double reads of neighboring spin orientations. To allow for parallel updates of the configuration in several tiles, these in turn need to be also arranged in a checkerboard fashion, leading to the two-level "double checkerboard" decomposition shown in the right panel of Fig.  $5.^{36,55}$  In this setup, one requires  $(L/T)^2/2$  thread blocks and each of them collectively updates one tile of the red shaded (coarse) sub-lattice shown in Fig. 5. After this kernel call has completed, a second call requests the same blocks to update the other coarse sub-lattice of tiles, thus completing a full sweep. Each block consists of  $T^2/2$  threads that collectively load the configuration of the tile from global memory into shared memory, with some of the threads additionally loading the one spin wide halo around the tile required to update the boundary spins correctly. After the load, all threads of the block are synchronized and then update the spins in shared memory in a checkerboard fashion as in the version without shared memory. Note that the two sub-lattices of a single tile are now updated from within the same kernel call.

- The full potential of this approach is only released if each tile, once loaded to shared memory, is subjected to several rounds of spin updates. If k rounds of updates are performed, the resulting "multi-hit" code is particularly economic on memory transfers and hence is able to fully

Fig. 7. Spin-flip times in ns of the double-checkerboard 2D Ising model GPU simulation code as a function of linear system size L and for tiles of size  $T \times T$  spins. The last data set is for runs on the GTX Titan Black GPU (Maxwell generation), whereas all other data is for the C1060 GPU (Tesla generation).

load the available computational units. This approach does not satisfy detailed balance, but the same applies to any checkerboard or sequential update, so this is no particular drawback of the method, but it needs to be taken into account when studying dynamical properties. It is clear, however, that very close to the critical point, the multi-hit approach will have slightly larger autocorrelation times than a single-hit variant as information can only be transmitted between tiles after each full update of the lattice. The resulting optimal choice of k was studied in some detail in Ref. [56] and found to be around k = 10 near criticality.

While for k = 1, the double checkerboard version of the code is slightly slower than the optimized variant not relying on shared memory ( $t_{\rm flip} =$ 0.081 ns on the Titan Black, reducing the speedup compared to the scalar CPU code to 75), for k > 1 one finds significantly improved performance yielding, for instance,  $t_{\rm flip} = 0.020$  ns for k = 100 (again for L = 4096). This is comparable to the results achievable with multi-spin coding.<sup>50</sup> We note that the tiling introduces as an additional parameter the tile size Twhich is limited by the maximum allowed number of threads per block (1024 on current devices, 512 for the Tesla C1060). The dependence of spin-flip times on tile size is illustrated for the C1060 GPU in Fig. 7. For more recent devices one finds the same trend. In general it is preferable to have larger blocks as this helps to maximize the number of resident

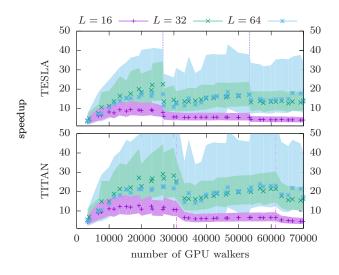

threads per multiprocessor (occupancy) which, in turn, generally improves the efficiency of the latency hiding mechanism. The strong dependence of spin-flip times on the lattice size L visible in Fig. 7 shows that for this type of problem optimal performance is only achieved for rather large lattices. For more recent GPUs which feature roughly 10 times more cores than the C1060, this effect is even more pronounced as is illustrated by the additional data for the GTX Titan Black GPU also shown in Fig. 7. The simulation of a single, small lattice system just does not provide enough parallelism to saturate the available parallel compute units — observations of this type led Gustafson to introduce the weak-scaling scenario as discussed in Sec. 2.1. As we shall see below, GPU codes for disordered systems or using generalized-ensemble simulation methods such as multicanonical or population annealing simulations do not have this problem and are able to fully load GPUs already for the smallest system sizes.

# 3.2. Random-hit algorithms

While the checkerboard update discussed in the previous section has the same stationary distribution as the random-site or sequential-update schemes, the dynamics of the different algorithms are not the same. Ideally, one would thus like to implement the physically most plausible random-site selection algorithm, but parallelizing it is a challenge as each single step typically is quite light computationally and so does not provide enough work for parallelization. If quantitative details of the dynamics are not of interest and the focus is on universal properties, for example in studies of domain growth,<sup>57</sup> it can be sufficient to concentrate on the checkerboard (or stochastic cellular automaton<sup>58</sup>) dynamics, which is typically closer to the behavior of the random-site algorithm than the sequential approach. If this is not sufficient or a time resolution of less than a full sweep is required, updates based on the standard checkerboard scheme are not suitable and, instead, a number of strategies for parallelizing the random-site selection update can be employed:

• Single-site updates are independent of each other, and can hence be implemented in parallel, if they occur further apart than the range of interactions. In a domain decomposition of the lattice (tiling), this can be guaranteed by excluding the sites at the boundary of each tile from update attempts (*dead border* scheme).<sup>59</sup> To allow these border sites to be updated as well and thus make the algorithm ergodic, the origin of the tiling is randomly shifted to a different location in periodic